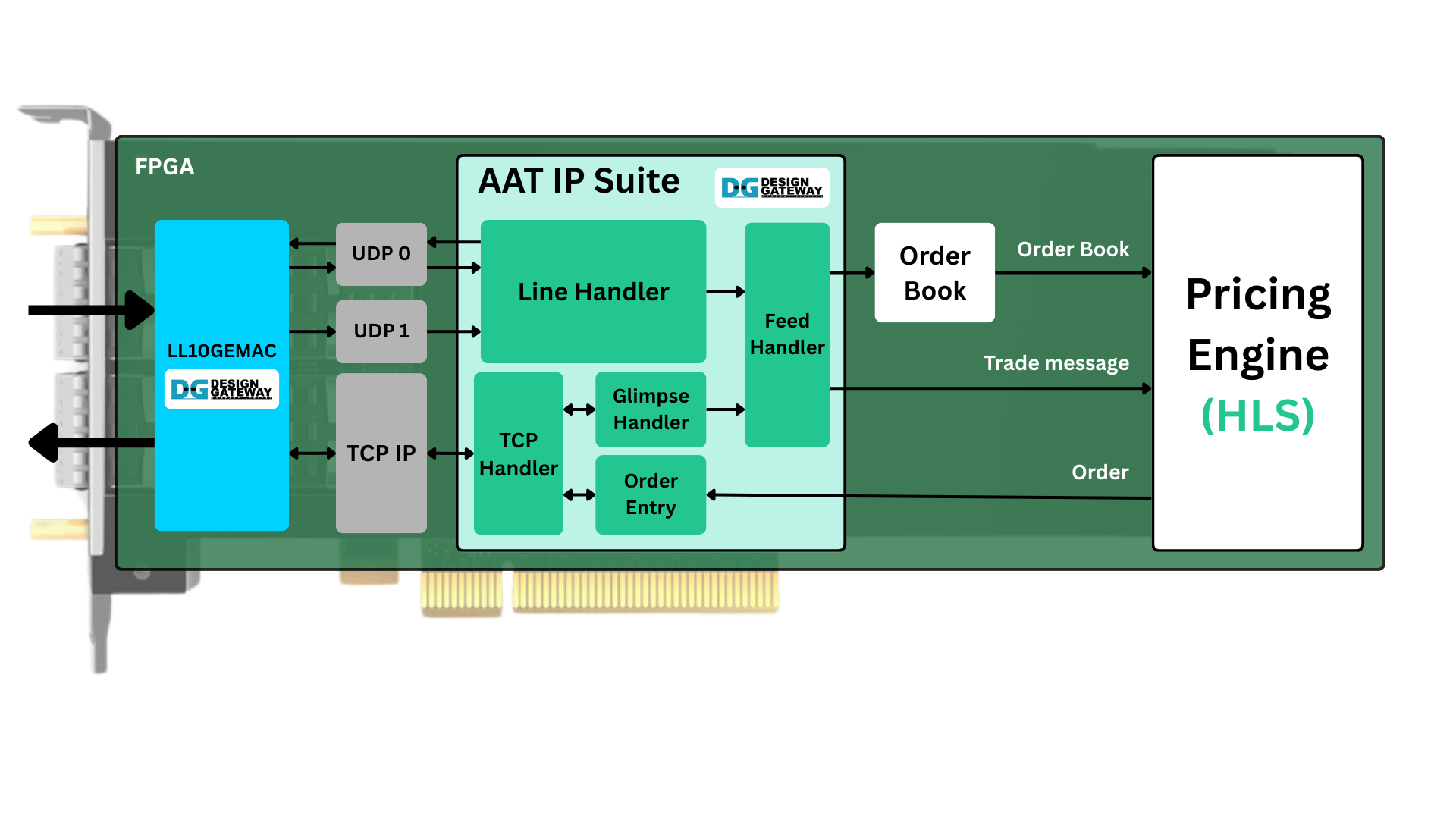

Hardware-Accelerated Network & Market Protocols

The platform consolidates all critical networking and market-protocol handling directly inside the FPGA to deliver predictable, low-latency performance.

Low-Latency Ethernet engine for wire-speed packet processing

TCP/UDP handled in hardware, avoiding kernel and driver overhead

ITCH decoder with integrated orderbook construction

OUCH order-entry formatter for immediate order submission

Support for SoupBinTCP and MoldUDP64 across major exchanges

Built-in heartbeat and session-state logic for stable connectivity